A Tutorial Introduction to VHDL Programming

A tutorial introduction to VHDL programming is a great way to learn this technology without having to take a computer science course or spend a fortune on a course. It covers the main concepts and terminology needed to get started. You will also learn the basics of data types, syntax, and structure. These will help you become familiar with VHDL and start making applications. This article will give you a good foundation for future projects.

Concepts

One of the key concepts to understand in VHDL programming is abstraction. As a result, a VHDL programming language has many features that are used in digital circuit design. For example, a VHDL program can be grouped into multiple levels of abstraction, each representing a component or activity in a design. In addition, these levels of abstraction can be used to implement parameterized reuse, data hiding, and object-oriented programming.

There are many architectures in VHDL, each representing a part of the overall design. The architecture is related to a circuit’s function and can be either an input or output interface. An entity can have multiple architectures, such as an RTL model for implementing design logic using registers, or a structural model for a gate level structure. The dataflow model, on the other hand, describes a single dataflow.

Structure

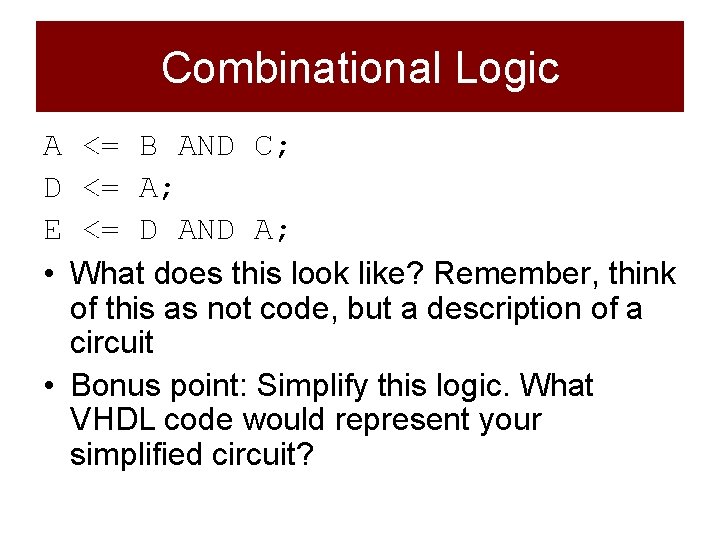

There are two different types of code in VHDL: structural and behavioral. Both types of code use a syntax similar to assembly language, but differ in the way they connect parts. The structural version is much simpler to read than the behavioral one, but still requires some basic knowledge of VHDL. In this article, we’ll look at structural versus behavioral VHDL programming to help you decide which is better for your application.

In a VHDL program, each design entity has a name and a file extension that starts with “.vhd.” Each entity has an entity declaration and an architecture body that describes how it will act. In addition to these two parts, the architecture body also defines the structure and behavior of the design coded in the VHDL program. Each entity can be composed of multiple entities connected together by interconnects.

Syntax

In VHDL programming, an entity is used to describe the components of the design. These entities represent inputs and outputs, so they must be modeled as black boxes. To define an entity, the first line of syntax includes its name, followed by a colon. A port declaration must include the name of the port, direction, and type. To end a VHDL entity declaration, use the semicolon.

Unlike Ada, VHDL uses many-valued logic to represent data. Instead of just bit-wise operation, the language can use 9-valued logic. This allows for powerful simulation and debugging. It is important to remember the syntax of VHDL when using it in your designs. The following examples illustrate some of the main features of VHDL. There are many other useful features of this programming language.

Data types

A VHDL program may use several data types to represent different things. Each type supports specific operations. A bit data type, for example, can support both arithmetic and logical operations. However, std_logic_1164 does not support arithmetic operations. In this case, the user must add or subtract data using the std_logic_arith package. Data types in VHDL may consist of either a built-in or a user-defined type.

In VHDL, data types can be either user-defined or predefined. A bit, for example, admits a value of 0 or 1. The assignment between object and value must be enclosed in single quotes. The example above shows a simple assignment between two types. The example uses a signal called ‘A’ and a signal called ‘B’. This is a data type.

Parameterized components

In VHDL programming, a generic function is used to create a generic component. This type of component is flexible and can be easily modified, regardless of the type of data it contains. This type of component is defined by a generic function and can be passed from block to block as a constant. The only difference between a generic function and a parameterized component is the type of data passed from block to block.

Arrays can be implemented using a standardized library of parameterized components. Sequential components, like shifters, registers, and counters, are often used as parameters in VHDL programming. These standardized libraries of shared models make it easier to reuse the components across different projects. The clk’event attribute expresses a changing edge of the clk signal. In the same way, the s’left and s’right attributes express the range of an array.

Simulation tools

A tutorial introduction to VHDL programming is a useful book for engineers and students who need a basic understanding of the language and how it is used to create electronic circuits. It helps readers create effective VHDL descriptions and simulate VHDL designs. It presents selected VHDL sample problems and explains each step of the solution. It also shows good VHDL code. It is also suitable for engineers who have no prior knowledge of VHDL programming.

A VHDL tutorial will also help you learn how to create modules and other fundamental digital design building blocks. Examples of these include multiplexer, flip-flop, and polar channel codes. In addition, this text provides a detailed explanation of the differences between clocked process and concurrent process, as well as real-time and simulation time. It is a helpful guide for designers and engineers who want to know how to create VHDL-based systems.